インバーターパラメーターとは何ですか?

インバーターのパラメーター設定は、パラメーターの意味を完全に理解していないため、最初に非常に重要です。さらに、リストされている設定パラメーターはさらに多く、圧倒的な方法があります。これらのユーザーの場合、インバーターパラメーター設定の基本的な知識を習得する必要があります。テスト実行前に設定する必要があるパラメーター、操作中に調整する必要があるパラメーター、および適切な調整範囲;デバッグプロセス中の不適切なパラメーター設定によって引き起こされる周波数変換を防ぐ方法デバイスの損傷など。

インバーターパラメーターの分類

1、工場設定を維持できるパラメーターを調整する必要はありません

試運転前の事前設定パラメーター

2.初期操作中に調整する必要があるパラメーター

3.一般的に使用されるインバーターパラメーターは

制御方法:

1、最小動作周波数:

2、最高動作周波数:

3、キャリア周波数:

4、モーターパラメーター:

5、周波数ホッピング:

6、加速および減速時間

7、トルクブースト

8、電子熱過負荷保護

9、周波数制限

10、バイアス周波数

11、周波数設定信号ゲイン

12、トルク制限

この記事は、電子部品、半導体、アンテナ、コンデンサ、コネクタ、ダイオード、トランジスタ、IC、抵抗器を提供するAllicdata Electronics Limitedの記事です

製品の詳細については、Webサイトにアクセスして入手してください。

Intel H61チップセット回路基板のリセットが機能します。

IntelシングルブリッジH61チップセットマザーボードリセット回路は、図1に示すように機能します。

図1 IntelシングルブリッジH61チップセットマザーボードのリセット回路の動作原理ブロック図。

1.ショートスイッチ、メインボード回路が動作を開始し、電源回路が降圧してメモリ電源、ブリッジ電源、バス電源、CPU電源などを生成します。

2. CPUの電源が安定すると、パワーマネージメントチップは高レベルのVR_RDY信号を出力します。回路がSYS _ PWROKブリッジに変換された後、CPUの電源が正常であることを示します。

3. ATXの出力電圧が安定した後、出力ATX_PWROK信号はIOチップまで遅延されます。 IOチップの内部変換後、PWROK高レベルフィードブリッジが出力されます。これは、ATX電源の電源が正常であることを示しています。

4.マザーボード機器がクロック信号を提供するために、ブリッジ内部クロック回路がオンになりました。

5.ブリッジ電源、クロック信号は正常であり、2つのPG信号を受信してDRAMPWRGD信号をCPUに送信し、メモリ電源が正常であることを示します。

6. CPUへのPROCPWRGD信号のブリッジ再出力は、ボード全体の電源が正常であることを示しました。

7.ブリッジはPLTRST#リセット信号を送信してIOチップをリセットし、ブリッジ内部遅延はPCIRST#リセットPCIスロットを送信します。

8.ブリッジからPLTRST#リセット信号を受信した後、IOチップは内部ロジック回路変換によりCPURST#リセットCPUを送信し、PCIRST1#リセットネットワークカードチップを送信し、PCIRST2#はPCL-をリセットします。 Eスロット。

この記事はAllicdata Electronics Limitedからのものです。

Welcomeの誘導エレクトロニクスの動作原理は何ですか?

電子技術の発展に伴い、純粋な電子技術を使用して多くのショッピングモールや一部のブランドストアでウェルカム機能を実現する電子ウェルカムデバイスが生産されるようになりました。

回路動作原理

人が歓迎装置の中を歩くと、影が生成され、フォトレジスタの耐光性の原理によってフォトレジスタの抵抗が変化します。センサーは、フォトレジスタ信号を受信することで生成されます。誘導電子ウェルカムデバイス回路の概略図を以下に示します。

誘導電子ウェルカム回路図

注:実際の生産プロセスでは、AC 220V電源が使用されます。特定の電力変換回路を設計してください。

誘導式電子ウェルカムデバイスはバッテリーで駆動され、システムは電源投入後に待機状態に入ります。光は遮られず、フォトレジスタRG1に直接照射されるため、RG1は抵抗値を示します。人体が光抵抗器に照射される光の一部を遮ると、光抵抗器が受ける光の強度が変化し、RG1の抵抗値が変化します。 RG1に流れる電流は、電解コンデンサC2を介して結合され、トランジスタQ1などの高利得により増幅された後、集積回路IC1の反転入力端子に入力される。この信号と非反転入力端子に入力された出力番号は、集積回路IC1で動作し増幅されます。

処理後、制御信号が形成されて集積回路IC1内のオーディオ生成回路が動作し、SP1を介して「こんにちは、ようこそ」オーディオ信号が生成され、電気音響変換が完了します。挨拶。

この記事はAllicdata Electronics Limitedからのものです。転載は、ソースを示す必要があります。

デジタル電子技術の回路の論理とは何ですか?

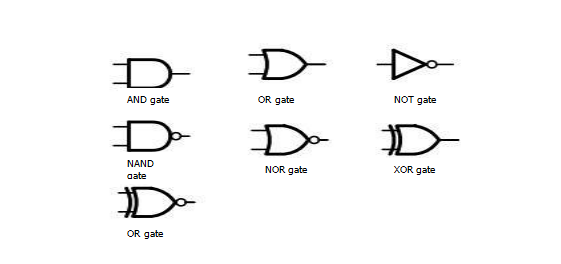

デジタル回路設計では、論理ゲートが最も基本的な演算ユニットであり、ANDゲート、ORゲート、およびNOTゲートが最も基本的な論理ゲートユニットですが、実際の設計で使用されるロジックは、多くの場合よりもはるかに複雑ですが、これらはすべて、AND、OR、およびNOTの組み合わせを使用して実装できます。たとえば、NAND、NOR、XOR、ORゲート。これらの論理ゲートのグラフィカルシンボルは次のとおりです。

ドアユニットを利用して回路を構築する方法は?

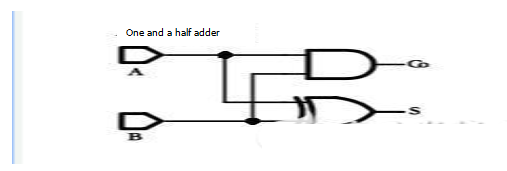

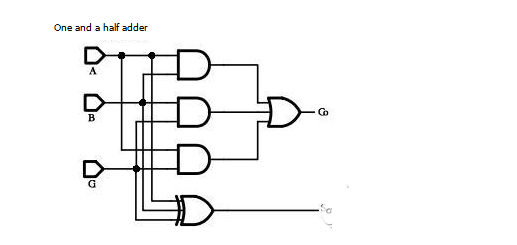

ゲートユニットによって構築された回路は、ゲート回路と呼ばれます。特定の論理関係に従って、必要な論理機能を実現するために異なるゲートユニットが接続されます。これがデジタル回路設計の目的です。以下に、論理ゲートユニットを使用して半加算器と全加算器のゲート回路を構築する2つの例を示します。

上記の図は、ANDゲートとXORゲートで構成される半加算回路です。AとBは半加算器の入力信号、Sは半加算器の結果出力、Cは半加算器のキャリー入力です。加算器。

上の図は、論理ゲートユニットによって構築された全加算回路です。 AとBは全加算器の入力信号、Ciは全加算器の桁上げ入力信号、Sは全加算器の結果出力、Coは全加算器の桁上げ出力です。

なぜ追加機能を実装できるのですか?以下は、上記の2つのゲート回路の加算機能の原理の簡単な分析です。最初に、半加算器と全加算器の違いを説明します。半加算器は、キャリーに関係なく入力信号AとBのみを加算します。全加算器は、AおよびBの加算に加えてキャリーCiを加算します。

そのうち、半加算器が追加され、AとBが両方とも1の場合にのみ、加算によりキャリーが生成されるため、Co = A&Bになります。 AとBの両方が0の場合、加算結果はS = 0です。 AとBの一方のみが0で、もう一方が1であるため、加算結果はS = 1なので、S = A ^ Bになります。

全加算器の操作はもう少し複雑です。 3つの入力A、B、およびCiの1つまたは3つが1の場合、加算結果はS = 1、それ以外の場合はS = 0であるため、S = A ^ B ^ Ci; 3つの入力A、B、Ciのいずれか2つまたは3つが1の場合、加算によりCo = 1のキャリーになります。それ以外の場合、Co = 0なので、Co = A&B | A&C | B&C

詳細を知りたい場合は、当社のウェブサイトには論理ゲート回路の製品仕様があります。ALLICDATAELECTRONICS LIMITEDにアクセスして詳細情報を入手できます。

IntelシングルブリッジH55チップマザーボード起動回路が機能します。

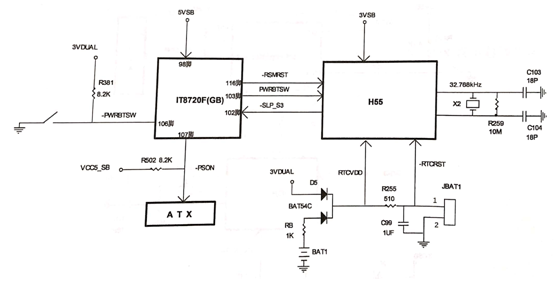

Intelマザーボード5シリーズチップセットは、サウスブリッジチップとノースブリッジチップの統合をPCH(プラットフォームコントロールセンター)に変更しました。 H5SSチップセットマザーボードブート回路は、図1に示すように、IOチップ、H55ブリッジチップ、RTC回路、スイッチピン、ATX電源インターフェイスで構成されています。

図1 Intel H55チップセットマザーボードブート回路の動作原理ブロック図。

IntelシングルブリッジH55チップセットマザーボードの基本原理は、Intelデュアルブリッジマザーボードの基本原理と基本的に同じです。マザーボードのブート機能は、IOチップとブリッジの支援により完了します。

第1段階:メインボードには、CMOSバッテリー、抵抗RBとダイオードD5を介して正のバッテリーが搭載され、ブリッジ内部リアルタイムクロック回路電源へのRTCVDDを生成し、抵抗R255とキャパシタンスC99がget-RTCRSTに遅延しますブリッジへのリアルタイムクロックリセット信号。ブリッジは水晶振動に電力を供給し、製品の振動は32.768kHzの周波数フィードブリッジを生成し始めます。ブリッジ内のリアルタイムクロック回路が機能し始め、CMOS設定を保存するために使用されます。

第2段階:ATX電源を差し込み、220V AC電源を接続します。 ATX電源は、5VSBスタンバイ電源を10OチップIT8720Fの98ピンに直接出力し、IT8720Fに電力を供給します。 5VSBは3VSBに変換され、ブリッジにスタンバイ電力を供給します。 IT8720Fチップに5VSBから電力が供給された後、内部遅延を通じてout-RSMRST高レベル信号がブリッジに送信され、スタンバイ電圧が正常であり、スタンバイ回路が終了したことが示されます。

3番目のステージ:ショートスイッチは、IT8720Fの106番目のピンに-PWIRBTSWトリガー信号を生成し、内部ロジック変換を介して103ピンから3.3V-0V-3.3Vのジャンピング信号PWRBTSWを出力して、ブリッジ要求に電源を投入します。ブリッジがPWRBTSW信号を受信し、そのスタンバイ状態が正常な場合、内部ロジック変換は3.3V-SLP_S3信号を出力します。この信号はIT8720Fの102番目のピンに送信され、電力が許可されていることを示します。 IT8720Fが-SLP_S3信号を受信すると、107ピン出力からの内部論理変換により、電源投入が完了します。

この記事はAllicdata Electronics Limitedからのものです。転載は、ソースを示す必要があります。

相補型金属酸化物半導体回路の構成と動作原理の略。

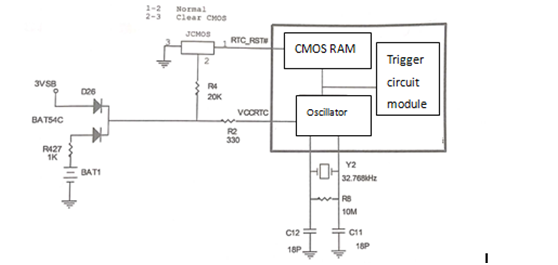

メインボードのCMOS回路は、主にCMOSランダムアクセスメモリ、リアルタイムクロック回路(RTC回路)、ジャンパー、サウスブリッジチップ、バッテリー、および電源で構成されています。回路など

図1 CMOS回路の構成。

電源が220Vに接続されていない場合、バッテリーの正極は抵抗R427を介してショットキーダイオードBATS4Cの正極に送られ、負極から出力されます。スタンバイ電源、メインボードを介してステップダウンして3VSBスタンバイ電源を取得し、BAT54Cの正極に送信し、負極の出力から抵抗R2を介してVCCRTCに改名し、オシレーター電源のサウスブリッジリアルタイムクロック回路に送信します。もう1つは抵抗R4を介してJCOMSジャンパーの2フィートに送信され、ジャンパーキャップによってプルされて、サウスブリッジへの高レベルRTC _ RST#信号を取得し、内部のCMOSランダムアクセスメモリをリセットしますサウスブリッジ:オシレーターが供給された後、外部Y _ 2クリスタルオシレーターが供給され、クリスタルオシレーターは32.768kHz周波数をサウスブリッジに生成し始めますVCCRTC、RTC _ RST#および32.768kHz周波数のSouブリッジが取得され、内部CMOS RAMが機能し始めます。

CMOS RAMの役割は、システムの日付と時刻、マザーボード上のメモリ設定のパラメーター、現在のシステムのハードディスクの構成、ユーザーが設定したパラメーターなどの重要な情報を保存することです電源投入時にシステムのセルフテストのためにBIOSによって初期化されます。

この記事はAllicdata Electronics Limitedからのものです。

回路基板が短絡しているかどうかを測定する方法は?

マザーボードが大幅に短絡しているかどうかを測定します。 3VSBスタンバイ電源、USBインターフェイスデータケーブル、CPU電源、メモリ電源、ブリッジ電源、バス電源などがあります。

測定短絡により、マルチメーターはダイオードの位置、赤ペンの接触接地、黒メーターのペン接触位置に接触し、ディスプレイ画面には測定ポイントと接地間のバイポーラ値の値が表示されます。

1. 3VSBがアースに短絡している場合。測定位置は、PCIスロットのA14フィートまたは境界のあるPCI-EスロットのB10フィートです。

(1)3VSBがグランドに短絡していることを確認したら、Nicチップを順番に取り外します。 1394、マザーボードIOチップの一部、固定出力3.3V 1117、サウスブリッジチップ。

(2)短絡が不確実な場合、スタンバイ状態のNicチップに触れることができ、IOチップ、Nanqiaoチップなどが高温であり、スタンバイ電圧が低いなど、3VSBが短絡しているかどうかを判断します。

2.ケーブルがアースに短絡している場合。地球に対する極の通常の値は約400〜600です。

(1)データラインのいずれかがグランドに短絡している場合、USBデータラインを測定し、サウスブリッジチップが不良であると判断します。

(2)USBデータラインを測定するには、データラインのいずれかが無限値の場合、まず破損したワイヤ間のサウスブリッジチップへのUSBインターフェース、破損したワイヤがサウスブリッジチップ空溶接またはサウスブリッジチップであるかどうかを確認します壊れた。

3. VCOREがグランドに短絡している場合。一般に、地球の双極子の値は30を超えていますが、正確な判断を比較する必要があります。短絡している場合は、まずFETがLD1010D、LD1014Dを使用しているかどうかを確認し、そうでない場合は、タンタルコンデンサ、電源チップ、下部チューブ、駆動チップ、フィルター容量、サウスノースブリッジチップの478メインボードなどを取り外します。

4.メモリ、AGPビデオカード、ブリッジ、バス電源などがグランドに短絡しているかどうか。チップグループは同じ値に似ていますが、0ではなく短絡を判定できません。比較方法を使用して判断します(テストスポット:コイル測定コイルピン、コイル測定電界効果管S極なし)。短絡が特定された場合、それは通常、ブリッジ短絡であり、めったに電界効果トランジスタとコンデンサの故障ではありません。

この記事はAllicdata Electronics Limitedからのものです