IntelシングルブリッジH55チップマザーボード起動回路が機能します。

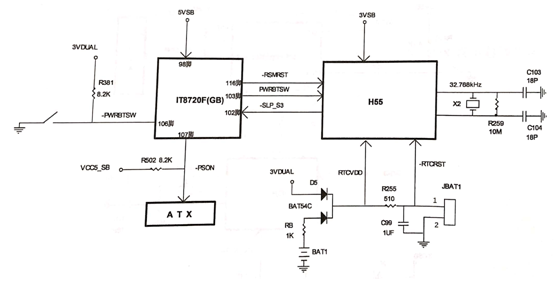

Intelマザーボード5シリーズチップセットは、サウスブリッジチップとノースブリッジチップの統合をPCH(プラットフォームコントロールセンター)に変更しました。 H5SSチップセットマザーボードブート回路は、図1に示すように、IOチップ、H55ブリッジチップ、RTC回路、スイッチピン、ATX電源インターフェイスで構成されています。

図1 Intel H55チップセットマザーボードブート回路の動作原理ブロック図。

IntelシングルブリッジH55チップセットマザーボードの基本原理は、Intelデュアルブリッジマザーボードの基本原理と基本的に同じです。マザーボードのブート機能は、IOチップとブリッジの支援により完了します。

第1段階:メインボードには、CMOSバッテリー、抵抗RBとダイオードD5を介して正のバッテリーが搭載され、ブリッジ内部リアルタイムクロック回路電源へのRTCVDDを生成し、抵抗R255とキャパシタンスC99がget-RTCRSTに遅延しますブリッジへのリアルタイムクロックリセット信号。ブリッジは水晶振動に電力を供給し、製品の振動は32.768kHzの周波数フィードブリッジを生成し始めます。ブリッジ内のリアルタイムクロック回路が機能し始め、CMOS設定を保存するために使用されます。

第2段階:ATX電源を差し込み、220V AC電源を接続します。 ATX電源は、5VSBスタンバイ電源を10OチップIT8720Fの98ピンに直接出力し、IT8720Fに電力を供給します。 5VSBは3VSBに変換され、ブリッジにスタンバイ電力を供給します。 IT8720Fチップに5VSBから電力が供給された後、内部遅延を通じてout-RSMRST高レベル信号がブリッジに送信され、スタンバイ電圧が正常であり、スタンバイ回路が終了したことが示されます。

3番目のステージ:ショートスイッチは、IT8720Fの106番目のピンに-PWIRBTSWトリガー信号を生成し、内部ロジック変換を介して103ピンから3.3V-0V-3.3Vのジャンピング信号PWRBTSWを出力して、ブリッジ要求に電源を投入します。ブリッジがPWRBTSW信号を受信し、そのスタンバイ状態が正常な場合、内部ロジック変換は3.3V-SLP_S3信号を出力します。この信号はIT8720Fの102番目のピンに送信され、電力が許可されていることを示します。 IT8720Fが-SLP_S3信号を受信すると、107ピン出力からの内部論理変換により、電源投入が完了します。

この記事はAllicdata Electronics Limitedからのものです。転載は、ソースを示す必要があります。